Community Newsletter: May 2012

IN THIS ISSUE:

- Message from Accellera Systems Initiative Chair

Shishpal Rawat talks about merger milestones and your call to action - Technical Committee Spotlight: The Unified Coverage Interoperability Standard

Article by Dr. Richard Ho and Dr. Ambar Sarkar, Co-Chairs of the UCIS Committee - Join Us at DAC

SystemC AMS BoF, SystemC Verification BoF, UCIS Lunch, SystemC Users Group / NASCUG XVIII - New Video Tutorial – UVM: Ready, Set, Deploy!

- DVCon 2013 Call for Abstracts

- Upcoming Events: SystemC Japan

- First Annual Leadership Award

Message from Accellera Systems Initiative Chair

It's been six months since Accellera and the Open SystemC Initiative joined forces to become Accellera Systems Initiative. A lot has happened in that time, and we've made significant progress investing in the technologies that accelerate the development and adoption of EDA and IP standards across various system-level domains. As we approach this year's Design Automation Conference, I'd like to share these achievements with you. I also invite you to join us at DAC for special industry events designed to promote information exchange and active collaboration of standards.

It's been six months since Accellera and the Open SystemC Initiative joined forces to become Accellera Systems Initiative. A lot has happened in that time, and we've made significant progress investing in the technologies that accelerate the development and adoption of EDA and IP standards across various system-level domains. As we approach this year's Design Automation Conference, I'd like to share these achievements with you. I also invite you to join us at DAC for special industry events designed to promote information exchange and active collaboration of standards.

Six Month Milestones

- Dec 5, 2011: Accellera and OSCI approve merger, unite to form Accellera Systems Initiative

Adopt charter to create EDA and IP standards to benefit electronic and semiconductor industries

- Overall attendance rose almost 10% to 834

- Exhibits were sold out with 35 exhibitors, including 8 first timers

View the video retrospective

Accellera Systems Initiative Day

- Four standards-based tutorials including UVM, SystemC, IP-XACT, United Coverage Interoperability Standard (UCIS)

UVM video tutorial now available >

- Town Hall lunch with interactive audience participation

- North American SystemC Users Group Meeting XVII

Presentations now available

Technical Excellence Award

- First-ever award presented to John Aynsley, Doulos, for outstanding contribution to SystemC standardization efforts

- Feb 21: Revised IEEE 1666 SystemC Language Standard for Electronic System-Level Design Is Available for Download at No Charge

The new version encompasses many enhancements, notably support for Transaction-Level Modeling (TLM), a critical approach to enable high level and more efficient design of complex ICs and SoCs

- Mar 12: SystemC AMS Draft 2.0 Standard to Advance Dynamic and Reactive Mixed-Signal System Design

Public review period has ended, but the draft of the AMS 2.0 standard is still available for download under the SystemC open-source license

- Apr 9-10: Indian SystemC User Group (ISCUG) conference held in Bangalore

Two hundred people in attendance; presentations now available

Join us at these Accellera Events at DAC

- Birds-Of-A-Feather Session - Analog Mixed-Signal

Tuesday, June 5, 7:00pm-8:30pm

- Birds-Of-A-Feather Session - SystemC Verification

Tuesday, June 5, 7:00pm-8:30pm

- Hosted Luncheon and Technical Presentation: Accellera Systems Initiative Rolls Out the Unified Coverage Interoperability Standard

Wednesday, June 6, 12:00-1:30pm

- SystemC Users Meeting - NASCUG XVIII

Wednesday, June 6, 2:00-6:00pm

Get Involved!

Get involved with Accellera Systems Initiative! Visit our website for recent developments and downloads of draft standards currently under review. Contact us if you are interested in starting a standards-based user group in your area. We're here to promote innovation through standardized interoperability and information exchange. We are counting on you to help shape the work that will set the foundation for the next generation of electronic products.

Sincerely,

Shishpal Rawat, Chair

Technical Committee Spotlight: The Unified Coverage Interoperability Standard

By Dr. Richard Ho and Dr. Ambar Sarkar, Co-Chairs of the UCIS Committee

After many years of dedicated work from both electronic design automation (EDA) vendors and members of the design community, the Unified Coverage Interoperability Standard (UCIS) version 1.0 will officially debut as an approved Accellera Systems Initiative standard at the Design Automation Conference 2012. The growing complexity of designs mandates that coverage data be shared among different tools to achieve full verification closure. UCIS is a first step towards the creation of a unified coverage standard that allows for interoperability of verification coverage data across multiple tools from multiple vendors. UCIS offers a standardized way to model and access verification coverage information.

UCIS is an industry initiative that has received contributions from EDA suppliers, EDA customers and facilitators. The participants all recognized that the community would benefit from a common and consistent application programming interface (API) and interchange format for coverage data as a step towards interoperability. Our vision is that standardization of the data interchange will enable innovation in both the EDA industry and in the design teams tackling the hardest verification problems. It is with pride that we count verification practitioners as well as all three of the major functional verification simulator companies as contributing members of this committee. Now that the standard has been released by Accellera, we hope to see UCIS help drive incremental productivity improvements through an emerging ecosystem of training, services, tools and new methods.

UCIS is an industry initiative that has received contributions from EDA suppliers, EDA customers and facilitators. The participants all recognized that the community would benefit from a common and consistent application programming interface (API) and interchange format for coverage data as a step towards interoperability. Our vision is that standardization of the data interchange will enable innovation in both the EDA industry and in the design teams tackling the hardest verification problems. It is with pride that we count verification practitioners as well as all three of the major functional verification simulator companies as contributing members of this committee. Now that the standard has been released by Accellera, we hope to see UCIS help drive incremental productivity improvements through an emerging ecosystem of training, services, tools and new methods.

The challenge that UCIS is addressing is that verification of complex electronic circuits frequently requires the utilization of multiple verification tools, possibly from multiple vendors, and the deployment of different verification technologies. Coverage metrics are critical to measure effectiveness and to highlight verification shortcomings that require attention. Each verification process generates one or more coverage metrics which may be disjoint, overlapping or subsets. One of the key roles of the verification team is to gather, merge and interpret this multitude of coverage data to provide an overall assessment of verification quality and progress toward providing complete validation. Currently, no single metric consistently and globally tells engineers the exact status of verification. However, one step in the right direction is to bring all types of coverage metrics into a single database that can be accessed in an industry standard way.

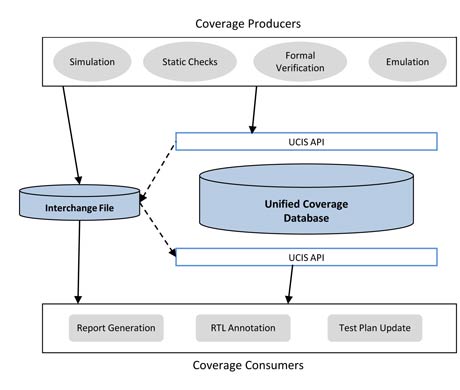

UCIS provides an API and a XML-based interchange format that enables the sharing of coverage data between coverage producers and coverage consumers. It is designed to operate across a variety of tools including software simulators, hardware accelerators, symbolic simulations, formal tools or custom verification tools. The UCIS coverage database (UCISDB) is conceptually a single repository of all coverage data from all verification processes. It may, however, be one or more physical files in non-volatile storage, and it may be implemented differently by different tools.

For design teams, productivity improvements will come from the use of the API and the interchange format within applications or scripts to implement functions that consume coverage data. For example, we might imagine applications that use the API and the interchange format for producing reports, annotating the design, merging of coverage data, ranking of tests, or updating verification plans. Some applications may manipulate the data and hence be both a consumer and a producer.

As verification and analysis technologies improve, the individual coverage producers or consumers may change. The database implementation may also change, but the standardized API and the interchange format are intended to allow them to continue to operate together.

To facilitate the sharing of applications and scripts that utilize UCIS, Accellera will host an open source repository where engineers and companies can make contributions to be shared with the community, improving the usefulness and benefits of UCIS for all.

Naturally, EDA vendors will need to implement the UCIS API interface and the XML interchange format in their tools. Major vendors including Cadence, Jasper, Mentor Graphics and Synopsys have pledged support for UCIS beginning this year (2012). Each vendor's specific roadmap has yet to be announced, but the fact that such endorsing commitments have been made is great for our industry and an enabler for greater design and verification productivity.

Discuss UCIS at the Accellera Systems Initiative DAC Luncheon on Wednesday, June 6 at 12:00-1:30pm.

Get involved! Join the UCIS Technical Committee.

Join Us at DAC

Birds-Of-A-Feather Meeting: At a crossroads – developing the next generation Analog/Mixed-Signal language standard(s)

Tuesday, June 5, 2012, 7:00-8:30pm

Moscone Center, Room 300

http://www.dac.com/additional+meetings.aspx?event=345&topic=5

Please sign up for this meeting in the Information Booth at DAC

Today's embedded and integrated systems interact more and more tightly with the analog physical environment, where digital HW/SW subsystems become functionally interwoven with analog/mixed-signal (AMS) blocks such as radio frequency (RF) interfaces, power electronics, or sensors and actuators. Examples are software defined radios, wireless sensor networks, and automotive applications, in which analog electronics are controlled, configured, or calibrated using digital techniques in hardware or software.

Historically, the hardware description languages Verilog-AMS and VHDL-AMS have addressed the analog implementation aspects but have limited capabilities to address the system-level design and verification challenges. From the digital perspective, SystemC and SystemVerilog focus on system-level design and verification, respectively. The SystemC AMS extensions are positioned to address the mixed-signal architectural design challenges, whereas SystemVerilog extensions are under development to include abstract analog signal representation in functional verification. Obviously, we are at a crossroads, where Verilog-AMS and VHDL-AMS are being updated and at the same time SystemC and SystemVerilog are expanding to support abstract AMS modeling styles. Should all of these AMS extensions remain compatible? Which elements are not yet addressed in the mixed-signal modeling and simulation domain but are essential for a next generation mixed-signal language? Can we focus on only one "mother HDL", or do we need more?

At this Birds-of-a-Feather session, these questions will be discussed and viable directions for the next step in AMS standards will be explored. AMS and RF system-level designers, circuit designers, verification engineers, and EDA vendors are invited to discuss the requirements and needs for the next-generation AMS languages.

Birds-Of-A-Feather Meeting: SystemC Verification

Tuesday, June 5, 2012, 7:00-8:30pm

Moscone Center, Room 304

http://www.dac.com/additional+meetings.aspx?event=350&topic=5

Please sign up for this meeting in the Information Booth at DAC

As the verification needs in SystemC change and communication with other languages is more and more frequent, evolution complementing the existing standards (such as the SCV library) are required. Many efforts already exist with this goal; research projects, new libraries, etc. The purpose of this event is to share experience, gather new requirements, use cases, and applications that will need to be pushed for standardization. This event is organized around the SystemC Verification Working Group community, but is open to everyone.

Hosted Luncheon and Technical Presentation: Accellera Systems Initiative Rolls Out the Unified Coverage Interoperability Standard

Speaker: Dr. Richard Ho, Co-Chair of the UCIS Committee

Please be Accellera Systems Initiative's guest at a luncheon where we will present the forthcoming Unified Coverage Interoperability Standard (UCIS).

Wednesday, June 6, 12:00-1:30pm

Moscone Center, Room 262

Register Now >

This luncheon is open to all DAC attendees. Seating is limited! You must pre-register for this event.

Coverage metrics are critical to measuring and guiding design verification. As designs have grown, increasingly advanced verification technologies, methods and additional metrics have been designed to form a fuller coverage model. There is currently no single metric that consistently and globally tells engineers the exact status of verification. But one step in the right direction is to bring all types of coverage metrics into a single database that can be accessed in an industry standard way. The UCIS facilitates the creation of a unified coverage database that allows for interoperability of coverage data across multiple tools from multiple vendors.

This presentation, intended for verification managers and tool developers alike, provides an introduction to and overview of the UCIS and how users plan to utilize it to enhance their verification flows. We provide a survey of many of the commonly-used coverage metrics and how they are modeled in the UCIS. The information that users will be able to access through the UCIS will allow them to write their own applications to analyze, grade, merge and report coverage from one or more databases from one or more tool vendors. We will also discuss the XML-based interchange format of UCIS, which provides a path to exchange coverage databases without requiring a common code library between tools and vendors.

| Sponsored by: |

NASCUG XVIII

North American SystemC User's Group Meeting

Wednesday, June 6, 2:00-6:00pm

Moscone Center, Room 262

Register Now >

This event is open to all DAC attendees. Seating is limited!

The North American SystemC Users Group (NASCUG) provides a unique forum for sharing SystemC experiences and knowledge among industry, research and universities. Stay tuned for an agenda at www.nascug.org.

New Video Tutorial -- UVM: Ready, Set, Deploy!

The Universal Verification Methodology (UVM) standard continues to gain adoption across the verification community. Presented by expert verification methodology architects and engineers at DVCon 2012, this eight-part video tutorial provides an introduction to key UVM concepts and best practices.

The Universal Verification Methodology (UVM) standard continues to gain adoption across the verification community. Presented by expert verification methodology architects and engineers at DVCon 2012, this eight-part video tutorial provides an introduction to key UVM concepts and best practices.

- Part 1: Base Classes in UVM

Tom Fitzpatrick, Mentor Graphics - Part 2: Communication and Sequences

John Aynsley, Doulos - Part 3: Customizing Your UVM Environment

Kathleen Meade, Cadence Design Systems - Part 4: Register Modeling in UVM

Adiel Khan, Synopsys

Real-life user experiences:

- Part 1: Getting Started with UVM

Vanessa Cooper, Verilab - Part 2: Stacking Verification Components in UVM

Stephen D'Onofrio, Paradigm Works

Peter J. D'Antonio, The MITRE Corp. - Part 3: OVM to UVM Transition

John Fowler, Advanced Micro Devices

Justin Refice, Advanced Micro Devices - Part 4: VC Building Blocks with UVM

Mark Strickland, Cisco Systems

Thanks to our Global Sponsors

for their support of NASCUG and the video tutorial production

|

|

|

|

|

|

DVCon 2013

Save the date for DVCon 2013

Save the date for DVCon 2013

February 25-28, 2013

DoubleTree Hotel, San Jose, CA

2013 Call for Abstracts now underway >

Thank you to our Steering Committee, Program Committee, attendees, and exhibitors for making 2012 a record-breaking year. See you next year at DVCon 2013.

Watch a brief video retrospective of the 2012 conference>

SystemC Japan

The third annual SystemC Japan Day will take place on July 6, 2012 in Shin-Yokohama, Japan.

The third annual SystemC Japan Day will take place on July 6, 2012 in Shin-Yokohama, Japan.

Shin-Yokohama Kokusai Hotel

South Building 2F

Shin-Yokohama, 3-18-1, 222-0033

www.systemcjapan.com

Participation is free. This popular event fills early, so register soon!

New! First Annual Leadership Award

Nominations are invited for the 2012 Accellera Systems Initiative Leadership Award, to be awarded to an individual who has provided active leadership and contributed significantly in the vision of EDA and IP standards development activities and the governance of Accellera Systems Initiative. A nominee can be anyone who has contributed to the leadership and vision of its standards.

Nominations will be accepted from Accellera members only. Please submit your candidate's name, affiliation, and qualifications to This email address is being protected from spambots. You need JavaScript enabled to view it. no later than May 21, 2012. The recipient will be recognized at our luncheon at DAC on Wednesday, June 6, 2012.

Get involved with Accellera Systems Initiative!

- Start a standards-based users group in your area.

- Become a Global Event sponsor of users group meetings and technical tutorials. Contact us!

ABOUT THIS NEWSLETTER

Newsletters are emailed to all Accellera Systems Initiative member employees and community participants. They contain news and event updates from accellera.org. If you do not wish to receive newsletters via email, you can unsubscribe in your account settings at www.accellera.org under the Workspace tab.

Add accellera.org to your list of acceptable domains to make sure you receive updates from Accellera Systems Initiative.

EDITORIAL CONTACT

If you have questions or need assistance, please contact:

Jill Jacobs

This email address is being protected from spambots. You need JavaScript enabled to view it.

Copyright 2012 Accellera Systems Initiative