Technical Activities

Technical experts from member companies all over the world participate in the development of Accellera System Initiative standards through the dedicated work of our Technical Committee. Companies around the world are using our standards for designing electronic systems such as printed circuit boards and integrated circuits (ICs) that have become an integral part of today’s "smart" devices.

Ongoing Technical Activities

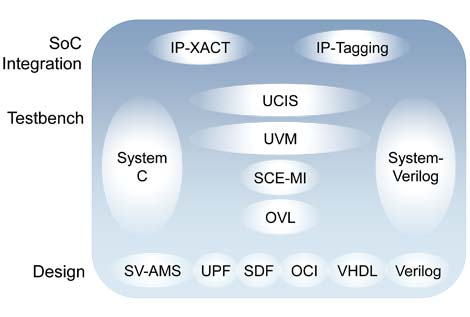

Design of silicon chips can be done at various levels of abstraction with technology standards factoring into each layer of design. Accellera Systems Initiative accelerates development of interoperable standards at the front end of the design process, from circuit design, where chips are conceptualized, to System-on-Chip (SoC) integration. Through common testbench technologies, such as verification, the continuity and integrity between the different abstraction levels of the chip are ensured. Standards developed by Accellera boost engineering productivity, increase chip functionality, lower power, and ultimately reduce the cost of electronic products to the overall consumer.

Accellera Systems Initiative

EDA and IP Design Standards and Initiatives

Accellera Systems Initiative Standards and Implementations

- Universal Verification Methodology (UVM) 1.1

- Open Verification Library (OVL) 2.7

- Standard Co-Emulation Modeling Interface (SCE-MI) 2.2

- Unified Coverage Interoperability Standard (UCIS) 1.0

- IP-XACT - Update of IEEE 1685 and Recommended Vendor Extensions

- Intellectual Property (IP) Tagging 1.0

- Multi-Language (launched)

- SystemC

- SystemC Synthesizable Subset Draft 1.3

- SystemC Transaction-level Modeling (TLM) 2.0*

- SystemC Analog Mixed-Signal (AMS) 2.0

- SystemC Configuration, Control & Inspection (CCI Requirements)

- SystemRDL 1.0

- Verilog-AMS (V-AMS) 2.3.1

- Open Source Companions:

- SystemC Reference Implementation 2.3.0 (* now includes TLM)

- SystemC Verification Library 1.0p2

- UVM Reference Implementation 1.1d

- Open Verification Library (OVL) 2.7

Download standards and implementations >

Completed IEEE Standards

- IEEE 1076: VHDL Language Reference Manual

- IEEE 1364-2005: Verilog Hardware Description Language

- IEEE 1450.6.1: Open Compression Interface (OCI)

- IEEE 1497: Standard Delay Format (SDF)

- IEEE 1666-2011: SystemC language

- IEEE 1685: IP-XACT

- IEEE 1800: SystemVerilog (SV)

- IEEE 1801: Unified Power Format (UPF)

- IEEE 1850: Property Specification Language (PSL)