# SystemC Community Update

ISCUG May 9, 2008 Girish Nanappa, OSCI

## **OSCI Membership**

Corporate **Members**

Associate

**Members**

ARM° cādence™ CoWare°

36 member companies, including 8 new since DATE 2007: CISC, CoFluent, ITRI, UPMC, STARC, TI, Maple DA, Virtutech

## **OSCI Organization**

Corporate Members

Associate Members

#### **Board Of Directors**

Officers Chairman

President Executive Director Treasurer Secretary

**Promotion Group**

**TLM Working Group**

**Language Working Group**

**Synthesis Working Group**

**Verification Working Group**

**Analog/Mixed-signal Working Group**

Governance

**Technical Activities**

## What's New at OSCI

## See us at DAC!

7th Symposium on Electronic System-Level Design with SystemC

Opening Session and Reception – North American SystemC Users Group Meeting Sunday, June 8, 4:00pm - 7:00pm

Panel Discussion: Real World Advantages of the OSCI TLM-2.0 Standard for Interoperability and IP Reuse

Monday, June 9, 12:00pm - 2:00pm; lunch provided

Special Workshop: OSCI TLM-2.0 in 2008 – A Leap Forward for Transaction-Level Modeling Standards

Monday, June 9, 2:00pm - 5:00pm

Free to industry professionals! www.systemc.org

# **Analog Mixed Signal WG**

- Requirement documentation for SystemC-AMS completed

- Identified application domains and target use cases

- (code) implementation requirements

- Interest in AMS WG is increasing

- Solid participation and contributions from semiconductor industry (4),

Universities (2), EDA vendor (2), Training (1) and Research (2) institutes

- Very successful public workshop in Dresden, June 2007:

"C/C++-Based Modeling of Embedded Mixed-Signal Systems"

- "Where 2 worlds meet: SystemC AMS and TLM interaction" at DATE 2008

- Definition of Language Reference Manual for AMS extension has started

- Additions: analogue-mixed signal synchronization, models of computation, ...

- Architecture and code review of SystemC-AMS prototype started

# **Synthesis Working Group**

- Target

- Working on synthesizable subset description

- Scope

- Mixed-level synthesis of SC\_CTHREAD and SC\_METHOD

- Schedule

- Updated draft planned for public review . . . soon

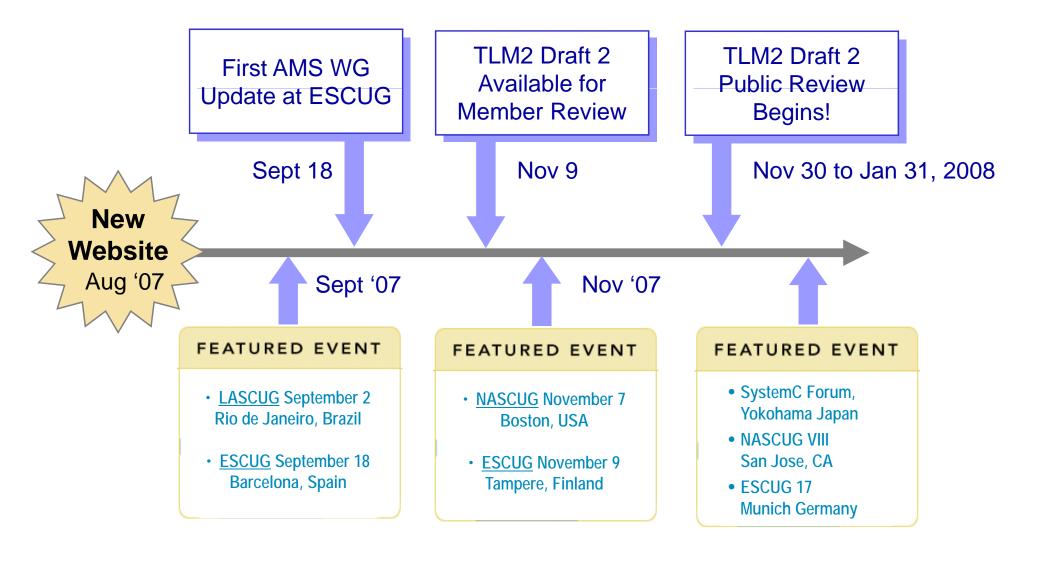

### **TLM WG in 2007**

- Thanks to Trevor Wieman (Intel) and Stuart Swan (Cadence) who served as chair and vice-chair

- Participation in the WG continues to be strong

- 18 organizations total

- Public review of TLM-2 Draft 1 was completed in February

- Detailed requirements spec released for public review in June

- TLM-2 Draft 2 released for public review in November

# TLM 2.0 Status <u>Update</u>

- TLM-2.0 Draft 2

- Available for public review on November 30<sup>th</sup>

- ◆ The public review period extended through January 31<sup>st</sup>

- OSCI tutorial at DVCon on February 19<sup>th</sup>

- Will recap feedback from public review

- OSCI Language Reference Manual (LRM)

- Will be based on TLM-2.0

- Work will begin after DAC 2008

- OSCI intends to pursue IEEE TLM standardization

- New WG leadership!

- Bart Vanthournout (CoWare) New Chair

- James Aldis (TI) New Vice-chair

## **TLM-2.0 Draft 2 Contents**

Cross-referenced to the requirements specification:

#### Mandatory Goals - Achieved!

- Untimed (UT) Modeling

- Loosely Timed (LT) Modeling

- Payload for Generic Memory-Mapped Bus

- Built-in Extension Mechanism

- Temporal Decoupling

- Non-intrusive Transactions

- Analysis Ports

- Documentation, Examples

#### Stretch Goals – Achieved!

- Model Synchronization

- Direct Memory Interface

#### Pulled in from TLM 2.1 – Achieved!

Approximately Timed (AT) Modeling

Not too late to download the kit and get up to speed!

## **Thanks to Our Global Sponsors**

OPEN SYSTEMC